### GaAs MMIC Non-Linear Transmission Line

#### **NLTL-6275**

#### 1. Device Overview

### 1.1 General Description

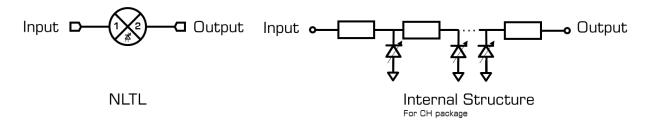

NLTL-6275 is a MMIC non-linear transmission line (NLTL) based comb generator. This NLTL offers excellent phase noise performance over a 3 to 15 GHz input frequency range with output tones beyond 85 GHz. NLTL-6275 is fabricated with GaAs Schottky diode based varactors on a 2.28 mm x 3.13 mm substrate. Both wire bondable die and connectorized modules are available.

Module

#### 1.2 Features

- Low Phase Noise

- Broadband Input Frequencies

- No External DC Bias Required

### 1.3 Applications

- Comb Line Generation

- High Efficiency Multiplication

- Samplers

- Phase Locked Loops

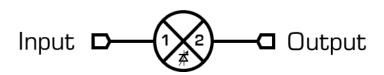

# 1.4 Functional Block Diagram

# 1.5 Part Ordering Options<sup>1</sup>

| Part<br>Number          | Description                                          | Package | Green Status | Product<br>Lifecycle | Export<br>Classification |  |

|-------------------------|------------------------------------------------------|---------|--------------|----------------------|--------------------------|--|

| NLTL-6275CH             | Wire bondable die                                    | CH      |              | Active               | EAR99                    |  |

| NLTL-6275U <sup>2</sup> | Connectorized<br>module, 1.85 mm<br>connector output | U       | RoHS         | Active               | EAR99                    |  |

| NLTL-6275U-<br>SW       | Connectorized<br>module; 1.0 mm<br>connector output  | U       |              | Active               | EAR99                    |  |

<sup>&</sup>lt;sup>1</sup> Refer to our <u>website</u> for a list of definitions for terminology presented in this table.

Copyright © 2018 Marki Microwave, Inc.

<sup>&</sup>lt;sup>2</sup> Performance on guaranteed to 67GHz.

# **Table of Contents**

| 1. | . Device Overview                        | 1 |

|----|------------------------------------------|---|

|    | 1.1 General Description                  | 1 |

|    | 1.2 Features                             | 1 |

|    | 1.3 Applications                         | 1 |

|    | 1.4 Functional Block Diagram             | 1 |

|    | 1.5 Part Ordering Options                | 1 |

| 2. | . Port Configurations and Functions      | 3 |

|    | 2.1 Port Diagram                         | 3 |

|    | 2.2 Port Functions                       | 3 |

| 3. | . Specifications                         | 4 |

|    | 3.1 Absolute Maximum Ratings             | 4 |

|    | 3.2 Package Information                  | 4 |

|    | 3.3 Recommended Operating Conditions . 4 | 4 |

|   | 3.4 Sequencing Requirements              | 4 |

|---|------------------------------------------|---|

|   | 3.5 Electrical Specifications            | 5 |

|   | 3.6 Typical Performance Plots            | 6 |

| 4 | . Application Information                | 9 |

|   | 4.1 Detailed Description                 | 9 |

|   | 4.2 Application Circuit 1                | 0 |

| 5 | . Die Mounting Recommendations 1         | 1 |

|   | 5.1 Mounting and Bonding Recommendations | 1 |

|   | 5.2 Handling Precautions 1               | 1 |

|   | 5.3 Bonding Diagram 1                    | 2 |

| 6 | . Mechanical Data1                       | 3 |

|   | 6.1 CH Package Outline Drawing 1         | 3 |

|   | 6.2 S Package Outline Drawing 1          | 3 |

# **Revision History**

| Revision Code | Revision Date  | Comment                        |  |  |

|---------------|----------------|--------------------------------|--|--|

| -             | September 2017 | Datasheet Initial Release      |  |  |

| А             | October 2017   | Corrected typos                |  |  |

| В             | December 2017  | Added U package outline        |  |  |

| С             | September 2018 | Corrected Signal Pad Locations |  |  |

# 2. Port Configurations and Functions

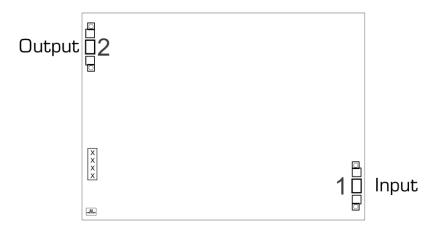

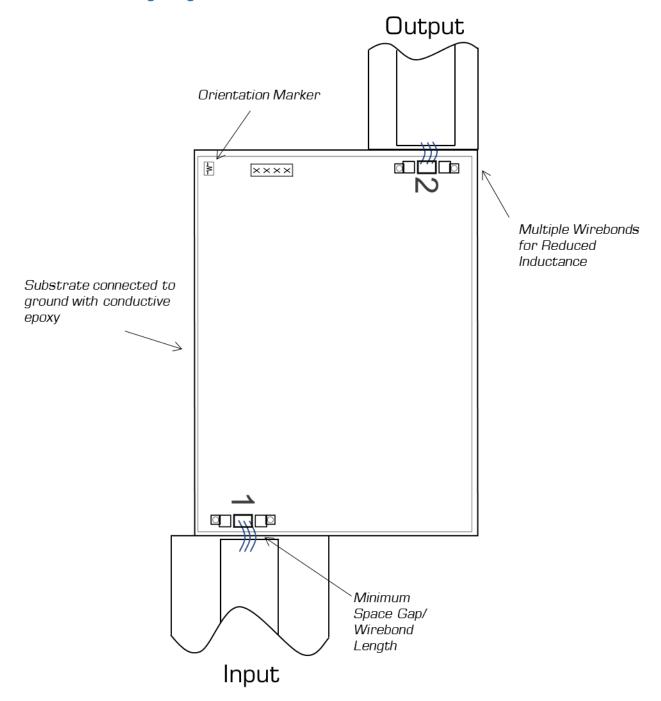

### 2.1 2.1 Port Diagram

A top-down view of the NLTL-6275's CH package outline drawing is shown below. The NLTL should only be used in the forward direction, with the input and output ports given in Port Functions.

#### 2.2 Port Functions

| Port   | Function | Description                                                                                                                                              | Equivalent<br>Circuit for Chip | Equivalent<br>Circuit for<br>Package |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|--------------------------------------|

| Port 1 | Input    | Port 1 is diode connected for the CH package and DC short for the U package.                                                                             | P1                             | P1                                   |

| Port 2 | Output   | Port 2 is diode connected for the CH and DC open for the U package.                                                                                      | P2~~~                          | P2                                   |

| GND    | Ground   | CH package ground path is provided through the substrate and ground bond pads. U package ground provided through metal housing and outer coax conductor. | GND∽_ੂ                         | GND○─                                |

### 3. Specifications

#### 3.1 3.1 Absolute Maximum Ratings

The Absolute Maximum Ratings indicate limits beyond which damage may occur to the device. If these limits are exceeded, the device may be inoperable or have a reduced lifetime.

| Parameter                   | Maximum Rating | Units |

|-----------------------------|----------------|-------|

| Port 1 DC Current           | TBD            | mA    |

| Port 2 DC Current           | TBD            | mA    |

| Power Handling, at any Port | +TBD           | dBm   |

| Operating Temperature       | -55 to +100    | °C    |

| Storage Temperature         | -65 to +125    | °C    |

### 3.2 **3.2 Package Information**

| Parameter                                           | Details   | Rating |

|-----------------------------------------------------|-----------|--------|

| ESD Human Body Model (HBM), per MIL-STD-750, Method |           | TBD    |

| Weight                                              | S Package | 10 g   |

#### 3.3 3.3 Recommended Operating Conditions

The Recommended Operating Conditions indicate the limits, inside which the device should be operated, to guarantee the performance given in Electrical Specifications Operating outside these limits may not necessarily cause damage to the device, but the performance may degrade outside the limits of the electrical specifications. For limits, above which damage may occur, see Absolute Maximum Ratings.

|                                      | Min | Nominal | Max  | Units |

|--------------------------------------|-----|---------|------|-------|

| T <sub>A</sub> , Ambient Temperature | -55 | +25     | +100 | °C    |

| Input Power                          | +16 |         | +26  | dBm   |

#### 3.4 3.4 Sequencing Requirements

This is a passive NLTL that requires no external DC bias. Self-bias of the diodes is sufficient for operation. It is not required, but is recommended to provide a  $50\Omega$  termination to each port before applying RF power.

### 3.5 3.5 Electrical Specifications

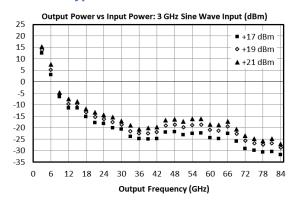

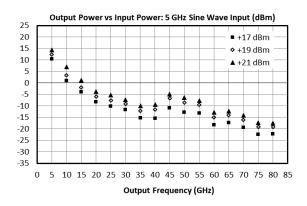

The electrical specifications apply at  $T_A=+25^{\circ}C$  in a  $50\Omega$  system. Typical data shown is for the NLTL used in the forward direction with a sine wave input.

Min and Max limits apply only to our connectorized units and are guaranteed at  $T_A=+25$ °C. All bare die are 100% DC tested and visually inspected.

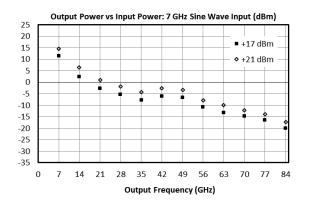

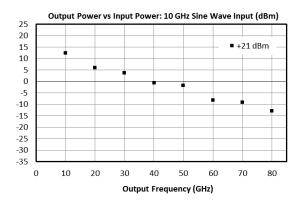

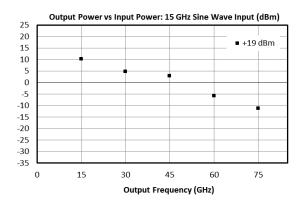

| Parameter                                               | Test Conditions | Min | Typical | Max | Units |

|---------------------------------------------------------|-----------------|-----|---------|-----|-------|

| Input (Port 1) Frequency Range                          |                 | 3   |         | 15  |       |

| Output (Port 2) Frequency<br>Range                      |                 | 3   |         | 85  | GHz   |

| Input Power                                             |                 | +17 |         | +26 | dBm   |

|                                                         | 3 GHz Input     |     |         | 28  |       |

|                                                         | 5 GHz Input     |     |         | 16  |       |

| Maximum Output Harmonic for given Input me <sup>3</sup> | 7 GHz Input     |     |         | 12  | -     |

| 3                                                       | 10 GHz Input    |     |         | 8   |       |

|                                                         | 15 GHz Input    |     |         | 5   |       |

Copyright © 2018 Marki Microwave, Inc.

$<sup>^{\</sup>rm 3}$  Maximum Output Harmonic specification given for the harmonic with a -20 dBm output power for a +20 dBm input.

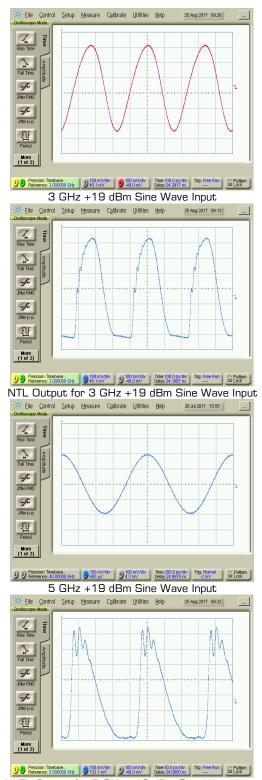

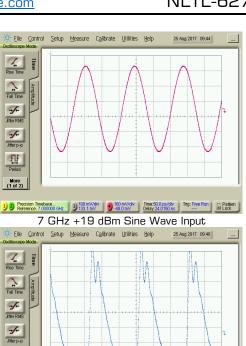

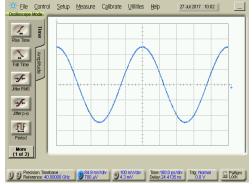

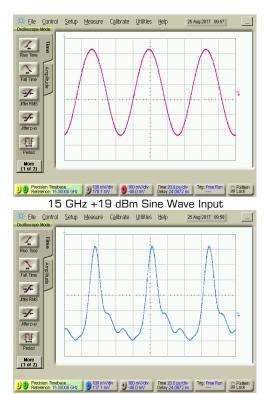

### 3.6 3.6 Typical Performance Plots

This space intentionally left blank

This space intentionally left blank

NLTL Output for 5 GHz +19 dBm Sine Wave Input

This space intentionally left blank

This space intentionally left blank

Period More (1 of 2)

10 GHz +19 dBm Sine Wave Input

NLTL Output for 10 GHz +19 dBm Sine Wave Input

This space intentionally left blank

NLTL Output for 15 GHz +19 dBm Sine Wave Input

# 4. Application Information

### 4.1 4.1 Detailed Description

NLTL-6275 belongs to Marki Microwave's NLTL family of multipliers and non-linear transmission lines. The NLTL product line consists of passive GaAs MMIC non-linear transmission lines designed and fabricated with GaAs Schottky diode based varactors. NLTLs take an input signal and create an impulse train of harmonics. Harmonic outputs up to and beyond 85 GHz are generated by the NLTL.

Port 1 supports S, C, and X band input signals. Port 2 will output integer multiples of the input signal (i.e., x2, x3, x4, ..., x28) up to the 28<sup>th</sup> output harmonic or a maximum of 85 GHz for a typical -20 dBm output power. Higher harmonics can be generated but will be at a lower efficiency.

The operating conditions of the NLTL are extremely important to optimize performance. High power inputs will increase the output power observed; however, the conversion efficiency will decrease. This is increasingly true for higher input frequencies and at input powers above the recommended limit.

NLTL-6275 requires no external DC bias. The self-bias of the diodes caused by the rectified RF input signal is sufficient for operation. For the best performance, optimization of the DC return path is recommended for each specific application to optimize the harmonic output power distribution.

The phase noise of a non-linear transmission line is outstanding. If verification of performance is necessary, the application circuit used and input conditions are extremely important. NLTLs are AM sensitive. If there is excessive AM noise on the input of the NLTL, observing the output of the NLTL will show excessive PM/phase noise because of the high AM to PM conversion property of NLTLs.

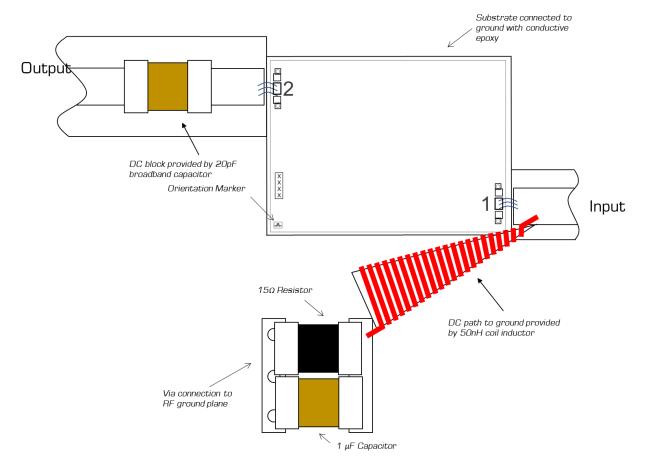

# 4.2 Application Circuit

**DC Path to Ground** — An RF choke followed by a 15  $\Omega$  resistor should be used to provide a DC path to ground on the input port of the NLTL. A shunt 1  $\mu$ F capacitor is used to filter noise generated by the resistor. This forms the circuit which self-biases the NLTL. The DC return to ground removes DC rectified current created by high power RF signal injection. The DC path to ground is provided within the S package. A conical coil inductor is recommended to push the self-resonance frequency of the inductor past the operating bandwidth of the NLTL. The recommended inductance value of the conical coil inductor is 50nH or higher.

**Blocking Capacitor** — A DC blocking capacitor on the output of the NLTL-6275's integrated circuit is necessary to prevent unwanted DC current flow from or to the output. If there is a DC signal on the input, place a DC block on the input to avoid disrupting the self-biasing of the diodes.

# 5. Die Mounting Recommendations

### 5.1 5.1 Mounting and Bonding Recommendations

Marki MMICs should be attached directly to a ground plane with conductive epoxy. The ground plane electrical impedance should be as low as practically possible. This will prevent resonances and permit the best possible electrical performance. Datasheet performance is only guaranteed in an environment with a low electrical impedance ground.

**Mounting** - To epoxy the chip, apply a minimum amount of conductive epoxy to the mounting surface so that a thin epoxy fillet is observed around the perimeter of the chip. Cure epoxy according to manufacturer instructions.

**Wire Bonding** - Ball or wedge bond with 0.025 mm (1 mil) diameter pure gold wire. Thermosonic wirebonding with a nominal stage temperature of 150  $^{\circ}$ C and a ball bonding force of 40 to 50 grams or wedge bonding force of 18 to 22 grams is recommended. Use the minimum level of ultrasonic energy to achieve reliable wirebonds. Wirebonds should be started on the chip and terminated on the package or substrate. All bonds should be as short as possible <0.31 mm (12 mils).

Circuit Considerations —  $50~\Omega$  transmission lines should be used for all high frequency connections in and out of the chip. Wirebonds should be kept as short as possible, with multiple wirebonds recommended for higher frequency connections to reduce parasitic inductance. In circumstances where the chip more than .001" thinner than the substrate, a heat spreading spacer tab is optional to further reduce bondwire length and parasitic inductance.

### 5.2 5.2 Handling Precautions

#### **General Handling**

Chips should be handled with care using tweezers or a vacuum collet. Users should take precautions to protect chips from direct human contact that can deposit contaminants, like perspiration and skin oils on any of the chip's surfaces.

### Static Sensitivity

GaAs MMIC devices are sensitive to ESD and should be handled, assembled, tested, and transported only in static protected environments.

Cleaning and Storage: Do not attempt to clean the chip with a liquid cleaning system or expose the bare chips to liquid. Once the ESD sensitive bags the chips are stored in are opened, chips should be stored in a dry nitrogen atmosphere.

# 5.3 5.3 Bonding Diagram

# 6. Mechanical Data

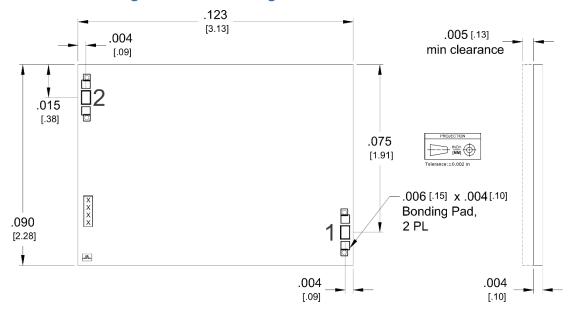

# 6.1 G.1 CH Package Outline Drawing

- 1. CH Substrate material is 0.004 in thick GaAs.

- 2. I/O trace finish is 4.2 microns Au. Ground plane finish is 5 microns Au.

- 3. XXXX denotes circuit number.

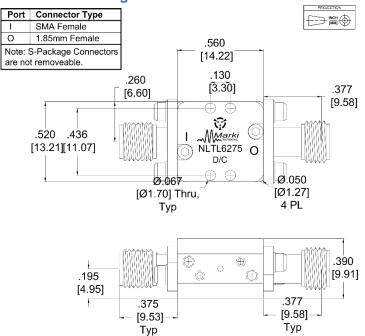

### 6.2 U Package Outline Drawing

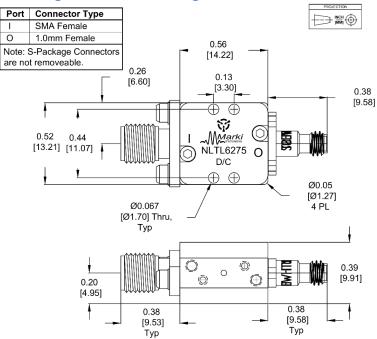

# 6.3 6.2 U-SW Package Outline Drawing

Marki Microwave reserves the right to make changes to the product(s) or information contained herein without notice.

Marki Microwave makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Marki Microwave assume any liability whatsoever arising out of the use or application of any product.